CustomLogic

Your own FPGA logic

At a glance

- FPGA design kit enabling the design and upload of FPGA code to a Coaxlink board

- Supported by Xilinx Vivado development tool

- Compatible with Coaxlink Octo, Coaxlink Quad CXP-12 and Coaxlink QSFP+: 70% of Xilinx Kintex Ultrascale XCKU035 FPGA resources available

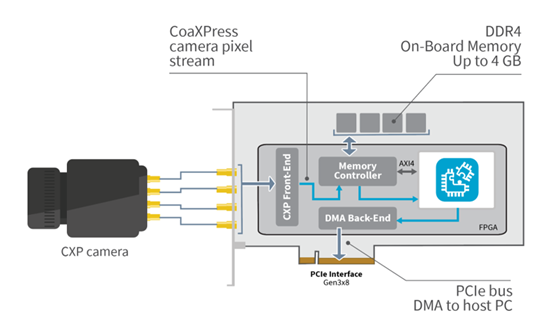

- Access to CoaXPress camera pixel stream, on-board DDR4 memory and PCIe Gen3 connectivity

- Memento Event Logging messaging

What is CustomLogic?

CustomLogic is an FPGA design kit enabling the design and upload of FPGA code to a Coaxlink board. It is compatible with the Coaxlink Octo, Coaxlink Quad CXP-12 and Coaxlink QSFP+. Typ. up to 70% of their Xilinx Kintex Ultrascale XCKU035 FPGA logic available. The design phase uses the Xilinx Vivado development tools (available free of charge from AMD-Xilinx).

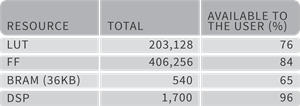

e.g. Resources available to the user of a Coaxlink Quad CXP-12 (1-camera, custom logic) firmware variant. Figures may vary for different firmware variants.

e.g. Resources available to the user of a Coaxlink Quad CXP-12 (1-camera, custom logic) firmware variant. Figures may vary for different firmware variants.

For PC3625 Coaxlink QSFP+ only: A specific IP License is required and obtainable from AMD. Contact our support for more information.

Data pixel Stream Interface

The Data Stream interface is based on the AMBA AXI4-Stream protocol. On the source side, this interface provides the user logic with images acquired from a CoaXPress Device (for example a CoaXPress camera). On the destination side, the Data Stream interface transfers the resulting images/data generated by the user logic to the PCI Express DMA Back-End channel.

DDRA4 Memory interface

The DDR4 Memory interface is based on the AMBA AXI4 protocol.

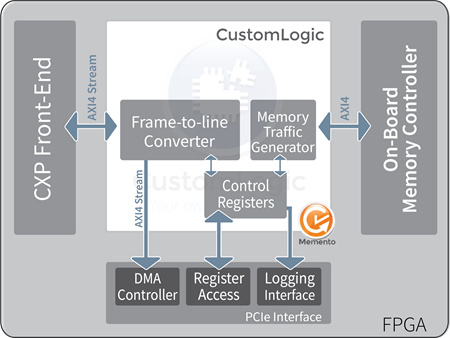

Memento Event interface

The Memento Event interface allows the User Logic to send timestamped events to the Memento Logging tool with a precision of 1 μs. Along with the timestamped event, two 32-bit arguments are reported in Memento.

Control/Status interface

The Control/Status interface allows the user to read and write registers inside the user logic via the Coaxlink Driver API.

Reference design

The Coaxlink CustomLogic SDK is delivered with a reference design intended to be used as a template. The reference design exposes all interfaces available to the user. It is a AMD Vivado project with the following functional block diagram:

Debugging

Using CustomLogic does not require any additional hardware. The 3613 JTAG Adapter AMD for Coaxlink (available free of charge from AMD) allows connecting the AMD programmer to the Coaxlink FPGA for debugging purposes.

Learn more about CustomLogic

Watch the tutorial on how to use CustomLogic

Learn how to use at its best the FPGA design kit in this tutorial from Paulo Possa.