CustomLogic

お客様独自のFPGAロジック

概要

- FPGAコードのデザインとCoaxlinkボードへのアップロードを実現するFPGAデザインキット

- Xilinx Vivado開発ツール対応

- Coaxlink Octo、Coaxlink Quad CXP-12、Coaxlink QSFP+対応: 70%のXilinx Kintex Ultrascale XCKU035 FPGAリソースを利用可能

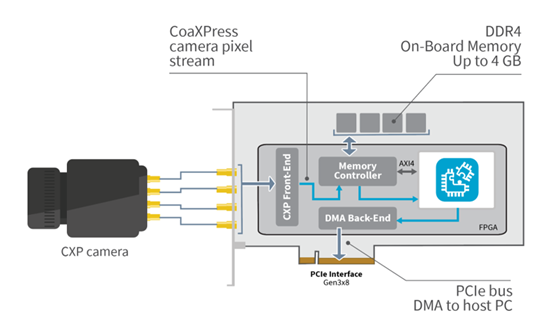

- CoaXPressカメラピクセルストリームへのアクセス、オンボードDDR4メモリ、PCIe Gen3との接続性

- Memento イベントロギングメッセージング

CustomLogicとは?

CustomLogicは、FPGAコードのデザインとCoaxlinkボードへのアップロードを実現するFPGAデザインキットです。Coaxlink Octo、Coaxlink Quad CXP-12、およびCoaxlink QSFP+との互換性があり、通常最大70%のXilinx Kintex Ultrascale XCKU035 FPGAロジックを使用できます。デザイン段階ではXilinx Vivado開発ツール(AMD-Xilinxより無料提供)を使用します。

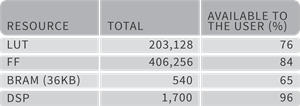

例: Coaxlink Quad CXP-12(1-camera, custom logic)ファームウェアバリアントのユーザーが使用できるリソース。数値は異なる場合があります

Coaxlink QSFP+の場合は、特定のIPライセンスが必要です。AMDから取得可能です。

データピクセルストリームインターフェイス

データストリームインターフェイスは、AMBA AXI4-Streamプロトコルに基づいています。このインターフェイスは、ソース側で、ユーザーロジックにCoaXPressデバイス(CoaXPressカメラなど)から取り込んだ画像を提供し、ターゲット側で、データストリームインターフェイスは、ユーザーロジックによって生成された結果画像/データをPCI Express DMAバックエンドチャンネルに転送します。

DDRA4メモリインターフェイス

DDR4メモリインターフェイスは、AMBA AXI4プロトコルに基づいています。

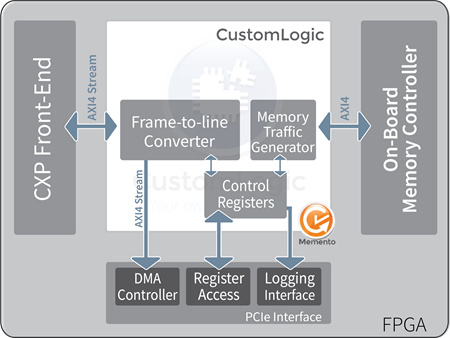

Mementoイベントインターフェイス

Mementoイベントインターフェイスを使用すると、ユーザーロジックは、1μs. の精度で、タイムスタンプ付きのイベントをMementoログ取得ツールに送信することができます。タイムスタンプ付きのイベントとともに、2つの32ビット引数がMementoに送信されます。

コントロール/ステータスインターフェイス

コントロール/ステータスインターフェイスによって、ユーザーは、Coaxlink Driver APIを介して、ユーザーロジック内のレジスタの読み取りと書き込みを行うことができます。

リファレンスデザイン

Coaxlink CustomLogic SDKには、テンプレートとして使用できるリファレンスデザインが含まれています。リファレンスデザインは、ユーザーが使用できるすべてのインターフェイスを紹介しています。AMD Vivadoプロジェクトで、次の機能ブロックダイアグラムが含まれています。

デバッグ機能

CustomLogicの使用には、追加のハードウェアは不要です。3613 JTAG Adapter AMD for Coaxlink(AMDより無料提供)を使用すると、AMDプログラマをCoaxlink FPGAに接続してデバッグ機能を使用することができます。

CustomLogicについて

CustomLogicの使用に関するチュートリアルを見る

こちらのPaulo PossaによるチュートリアルでFPGAデザインキットを最大限に活用する方法をご覧ください。